Speedgoat FPGA板卡使用系列文章之集成外部IP软核

前言

HDL Coder 是MathWorks公司提供的支持用户在MATLAB/Simulink环境中实现FPGA算法开发实现的专用工具箱。通过使用此工具箱,用户可以脱离传统开发流程中硬件描述语言VHDL或Verilog代码的编写,在Simulink模型中通过拖拽连接HDL Coder工具箱中的基本模块构成FPGA算法模型。FPGA模型搭建完成之后,可以通过HDL Coder将FPGA模型转换为VHDL或Verilog代码,然后再通过调用Vivado或ISE(硬件平台为Xilinx公司产品情况下)综合实现。

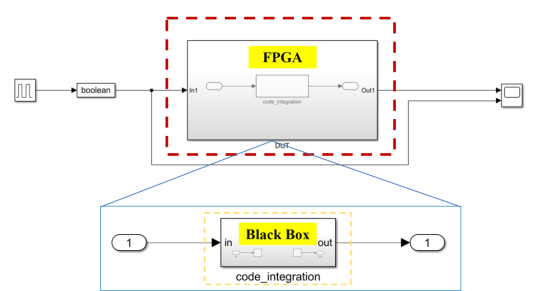

图1

在一些工程开发中,用户可能会集成一些外部已有HDL代码到新开发的FPGA模型中,这些代码可能是:

1. 手动编写或其他工具生成的VHDL或Verilog代码;

2. 第三方IP核;

3. 由HDL Coder生成的其他代码。

通过集成这些已验证过的HDL代码,可以减小Simulink中搭建相同功能的FPGA模型的难度,节省开发时间。在Simulink模型中可以通过Black Box来实现外部代码的嵌入集成。

本文将具体阐述Black Box的使用,来说明如何在Simulink中集成已有HDL代码,加速FPGA的开发。

Black Box

1.Black Box的创建

在HDL Coder中,1块FPGA板卡的应用以1个subsytem的形式呈现在Simulink模型中,且此子系统中的所有算法都必须使用HDL Coder支持的相关工具箱中的模块搭建。在此子系统中的算法都会被下载到FPGA中高速并行执行,而子系统之外的算法会被下载到CPU中串行执行。任意一个嵌套了外部编码的Black box也是以子系统的形式存在于FPGA子系统中。如下图:

图2

2.Black box的具体创建过程如下

- 从HDL Coder工具箱中拖取一个虚拟或原子子系统到FPGA子系统中,根据需要进行命名;

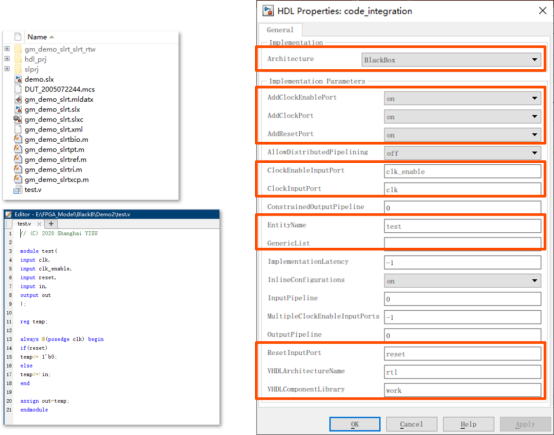

- 选中子系统,鼠标右键选择HDL Code> HDL Block Properties:(如图3)

- 图3

- 对属性参数进行定义:(如图4)

图4

主要设置的参数如下:

|

属性参数 说明

|

|

|

Architecture |

设置为BlackBox用于集成外部编码 |

|

AddClockEnablePort |

使能或禁用Clock Enable输入端口,此例中指定为on |

|

AddClockPort |

使能或禁用Clock输入端口,此例中指定为on |

|

AddResetPort |

使能或禁用Reset输入端口,此例中指定为on |

|

ClockEnableInputPort |

如使能Clock Enable输入端口,在此指定端口名称,注意要与代码中定义的名称一致,此例中指定为clk_enable |

|

ClockInputPort |

如使能Clock 输入端口,在此指定端口名称,注意要与代码中定义的名称一致,此例中指定为clk |

|

ResetInputPort |

如使能Reset输入端口,在此指定端口名称,注意要与代码中定义的名称一致,此例中指定为reset |

|

EntityName |

指定嵌入代码的entity或module名称,此例中定义的module名为test |

|

GenericList

|

指定类属参量表,以字符串形式 |

|

VHDLArchitectureName VHDLComponentLibrary |

如嵌入VHDL代码,根据VHDL代码指定对应结构体名和库 |

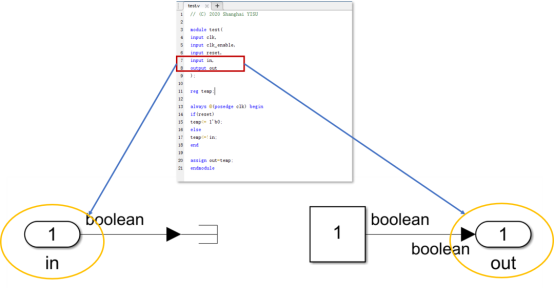

4. 根据要集成的module或entity中定义的数据input和output接口给Black Box子系统定义inport和outport,名称、方向和数据类型要一致(如图5):

图5

如此1个Block Box接口子系统即定义完毕。

外部代码集成

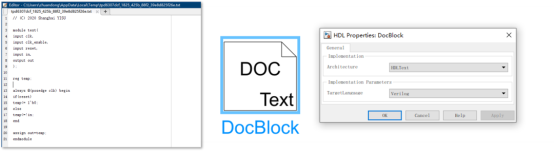

外部已有HDL代码的集成有两种方式:通过DocBlock集成或通过HDL Workflow Advisor添加。

1. DocBlock:如用户希望将FPGA模型和外部代码合并管理,则可通过DocBlock实现。在HDL Coder工具箱中,找到DocBlock模块,添加到Black Box子系统中,鼠标右键选择HDL Code> HDL Block Properties,将Architecture选择为HDLText,TargetLanguage选择为要集成的代码语言。然后再双击DocBlock模块进入编辑界面,将外部代码拷贝进去即可。如下图:

图6

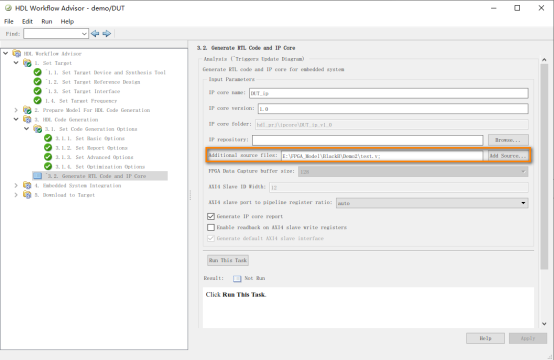

2. 通过HDL Workflow Advisor添加:此种形式下,Black Box无需添加DocBlock模块,在模型编译阶段,通过HDL Workflow Advisor添加Black Box 属性中指定的entityname对应的代码。如下图:

图7

如此外部代码即通过Black Box集成到FPGA模型中。

外部代码综合实现

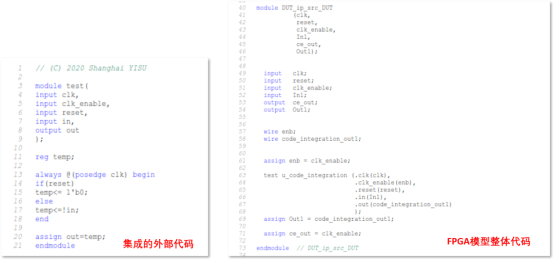

通过HDL Workflow Advisor对FPGA子系统进行HDL代码生成以及最终的综合实现,产生的源文件包含整体FPGA模型的代码文件以及集成嵌入的代码文件,从整体代码来看,被集成的Verilog module已被成功例化。

图8

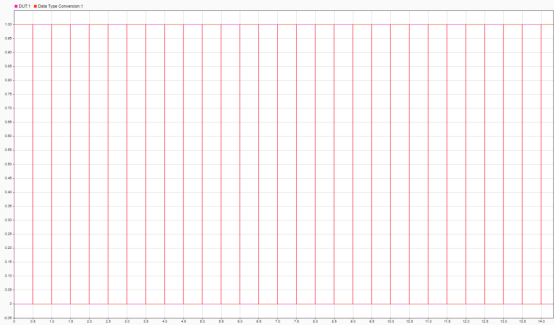

将最终生成的位流文件下载到Speedgoat IO397 FPGA板卡中实时运行,集成的外部代码功能为将输入的信号取反然后输出,从最终的实验结果来看,输入和输出的波形反相,集成的外部代码被成功实现。

图9

HDL Coder还支持Testbench的生成与ModSim实现联合仿真验证,时序的自动化分析、自动化流水线技术以及时序和面积的优化等功能(访问MathWorks官网,了解更多HDL Coder相关信息:https://ww2.mathworks.cn/products/hdl-coder.html)。