Speedgoat FPGA板卡使用系列文章之IO端口调用

前言

Speedgoat的可编程FPGA板卡可以利用MATLAB的HDLCoder在Simulink环境下搭建模型对其进行编程,并且通过HDL Workflow Advisor 进行位流文件(烧写进实时仿真机的二进制文件)生成前的环境配置,模型检查,模型输入输出端口与硬件端口的匹配,位流文件生成的过程的指导。

在利用HDL Coder建模过程中需要注意模拟输入(AI)触发(Triger)端口和转化完成(Valid)端口的模块搭建和与硬件端口的映射,模拟输出(AO)端口的(Triger)、转化完成(Valid)(注:模型中用Ready表示)端口的模块搭建和与硬件端口的映射。最后讲解数字输入口如何避免或者减小亚稳态情况的出现。

模拟端口的FPGA建模方法

u 模拟量的回环测试模型

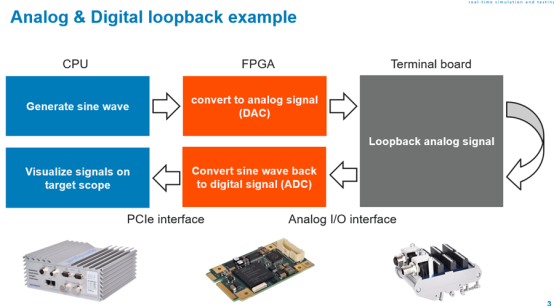

本例以图1为例,介绍模拟端口的FPGA建模方法。

图1

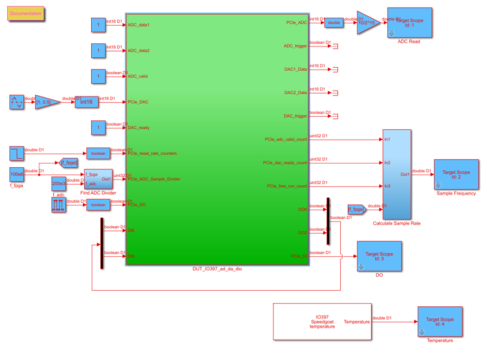

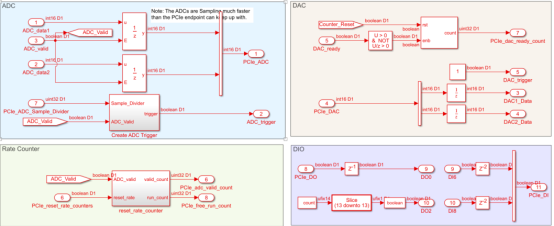

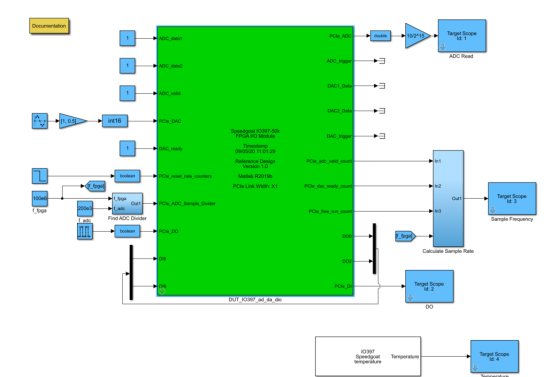

FPGA模型展开如图2:

图2

绿色模块的外围模块是要下载到CPU中的模型,绿色模块是要下载到FPGA芯片中的模型。回环测试的逻辑是在CPU模型中产生一个固定频率的正弦波,通过PCIe总线传递到FPGA芯片中,然后利用AO输出,通过硬线连接再将该模拟量通过AI端口引入到FPGA芯片中,通过PCIe总线传入CPU,进行可视化显示。具体的逻辑如图3所示

图3

u 模拟信号值的范围

对于可编程FPGA板卡而言,模数转换器(ADC)/数模转换器(DAC)的输入和输出的信号在模型层面的的数据类型为int16,int16能够覆盖到ADC/DAC的电压范围。Speedgoat的大多数的FPGA板卡ADC/DAC的输入或者输出电压是软件可配置的。

如果某一板卡的模拟信号范围被设置为±10V,上下阈值的插值也就是20V,那么模数转换器(ADC)/数模转换器(DAC)的精度为20V/216 = 305µV。

基于此,建模的时候对于输入ADC/DAC的输入输出信号的类型要设成int16的数据类型。

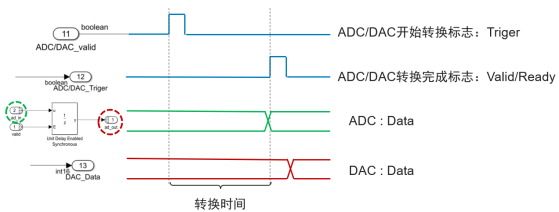

u 模拟信号的Triger和Valid信号建模

Triger信号:ADC/DAC控制器的工作需要待测模型的特定端口进行触发,如果触发端口被设为常数1也就是持续触发,那么ADC/DAC将工作在最大速率。也可以通过模型算法其触发端口产生周期性的脉冲,但是脉冲频率要小于等于ADC/DAC的最大工作频率。

Valid信号:ADC/DAC被触发后,就开始进行模数或数模的转化,转化完成以后便会产生一个转换完成标志Valid信号,标志着信号转换完成。

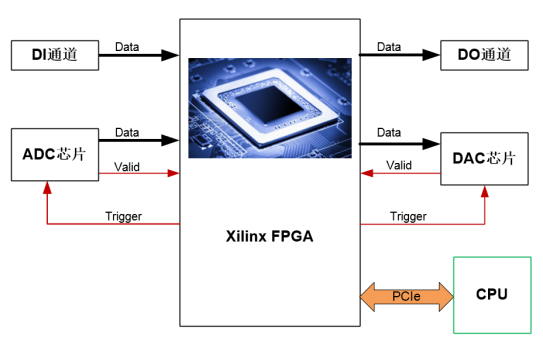

以IO397为例,该板卡有4路ADC和4路DAC。板卡的基本框架如图4:

图4

ü ADC(1:4)AXIS SLAVE:Data

IO397I/O模块提供4路同步采样16位/ADC数据通道。数据类型为int16,方向为输入。

ü ADC (1:4) AXIS Slave: Triger

因为ADC是同步采样,所以通道1到4共用一个Triger信号。当端口产生triger信号时,触发ADC进行模数转换,当转换完成Valid端口产生一个脉冲信号。数据类型为boolean,方向为输出。该信号由待测模块产生。

ü ADC (1:4) AXIS Slave: Valid

因为ADC是同步采样,所以通道1到4共用一个Valid信号,模数转换完成后产生一个完成脉冲标志Valid信号。数据类型boolean,方向输入。该信号由待测模块使用。

ü DAC (1:4) AXIS Master: Data

IO397I/O模块提供4路同步更新16位DAC数据通道。数据类型为int16,方向为输出。

ü DAC (1:4) AXIS Master:Triger

因为DAC是同步更新,所以通道1到4共用一个Triger信号,当端口产生Triger信号时,触发DAC进行数模转换,当转换完成Ready(Valid)端口产生一个脉冲信号。数据类型为boolean,方向为输出。该信号由待测模块产生。

ü DAC (1:4) AXIS Master: Ready(Valid)

因为DAC是同步更新,所以通道1到4共用一个Ready信号,数模转换完成后产生一个完成的脉冲标志Ready信号。数据类型为boolean,方向为输入,该信号被待测模块使用。

信号时序图如图5所示:

图5

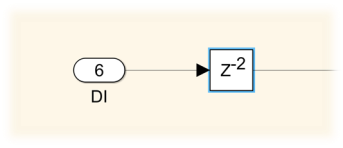

数字端口的FPGA建模方法

数字输入信号一般与FPGA时钟是异步的,所以为了避免输入信号出现亚稳定状态,数字输入信号需要通过延迟模块与FPGA时钟保持同步。单位延迟的数量越多,亚稳态出现的可能性就越小。

图6

任何触发器都可以很容易地实现亚稳态。将它的数据输入与时钟的采样边缘同时切换,就会得到亚稳态。

两个亚稳态之间的平均时间可以如下式表示

|

|

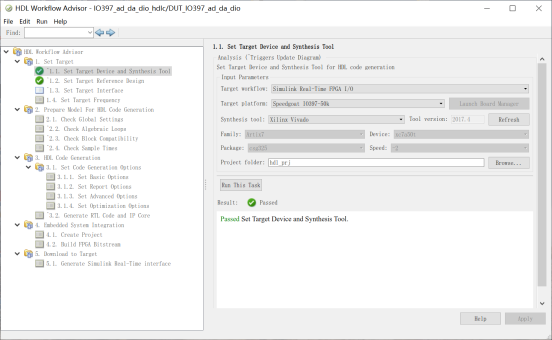

HDL Workflow Advisor中进行端口匹配

u 注意点

1. 将FPGA模型编译成位流文件需要调用Vivado的编译器,Vivado不能识别长路径,所以要尽可能保持MATLAB的工作路径短一些。

2. 确保安装了Vivado软件的证书。

3. 启动HDL Workflow Advisor之前要首先指定Vivado编译器的路径,指定方法:在命令行输入:hdlsetuptoolpath('ToolName','XilinxVivado','ToolPath', 'C:\Xilinx\Vivado\2017.4\bin'),其中C:\...”为Vivado的编译器的路径。

4. Vivado版本要与当前使用的MATLAB版本要对应起来,如果版本不对应的话,暂时又没有安装对应版本的Vivado时,可以在HDL Workflow Advisor的1.2中勾选Ignore tool version mismatch。

u 主要设置过程

1. 在FPGA的系统模型上右键选择HDL Workflow Advisor

2. 设置目标板类型和综合工具:步骤1.1。

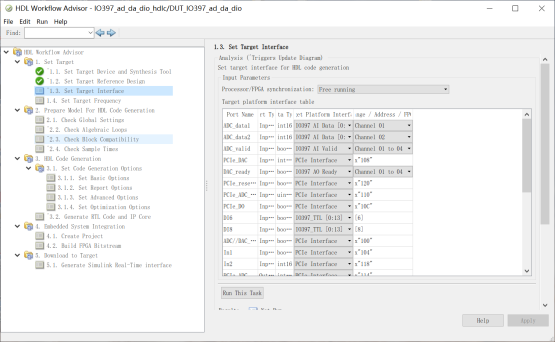

3. 映射模型端口到硬件端口上:步骤1.3。

4. 设置目标频率:步骤1.4。

5. 配置代码生成的各种参数:步骤3。

6. 各个步骤右键点击运行,检查模型及配置是否满足位流文件生成的要求。也可以一键同一运行。

图7

图8

运行通过后,生成用于下载到实时目标机中的模型,如图9所示。

图9

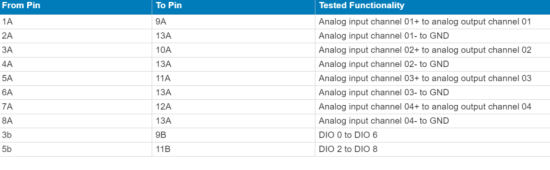

对实时机的硬件接口进行连接,连接定义如图10所示。

图10

输出结果如图11所示

图11

以上是Speedgoat系统关于可编程FPGA板卡中模拟量和数字量接口使用方法的介绍,如果使用中遇到疑问,欢迎与熠速联系。